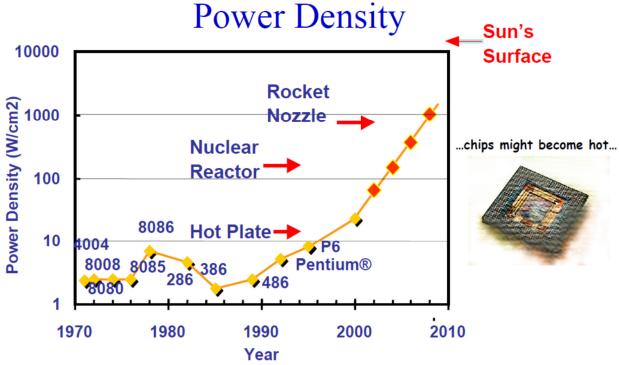

## Sviluppo tecnologico dell'elettronica digitale:

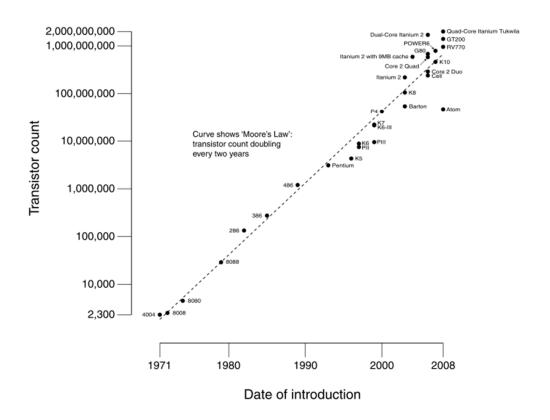

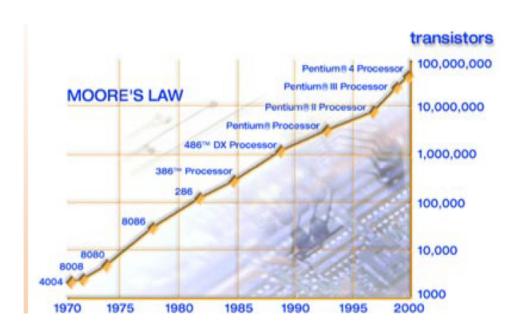

## CPU Transistor Counts 1971-2008 & Moore's Law

## Prestazioni e problemi:

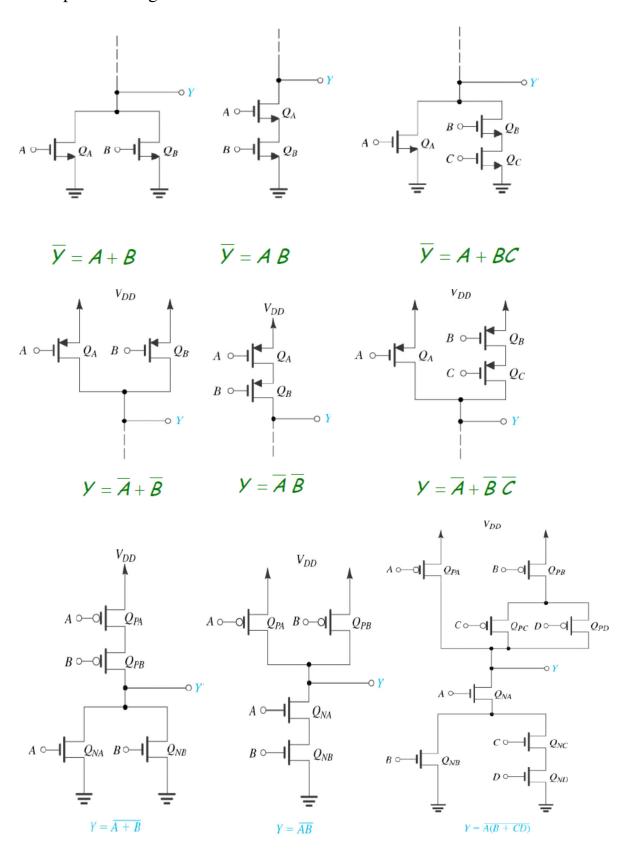

## Famiglia logica:

Insieme di gates che svolgono le funzioni logiche elementari basata su prefissati livelli logici (tensione/corrente), tecnologia (BJT/MOS), tempi di commutazione, capacita' di interconnessione (pilotaggio/bus/...), etc → Insieme di circuiti integrati direttamente interconnettibili

```

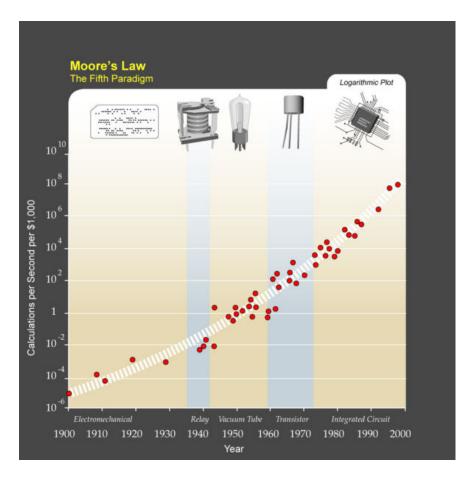

Inizio '900: Rele'

(es. centralini telefonici, Z3 (Germania - 1941))

Anni '40-'50: Tubi a vuoto

(es. ENIAC (US - 1946))

Anni '60: Transistor bipolari

(Discreti, poi integrati - Es. RTL, DTL, TTL,...)

Anni '70 - '80: PMOS, NMOS

(Zilog Z80, Intel 8080, Motorola 6502, Fairchild F8, ..)

Anni '90 → : CMOS

~ Tutto!

```

Proprieta' fondamentale di ogni famiglia logica: Tutti tipi di gate basati su un'unica funzione logica fondamentale: NOT Circuito che esegue la funzione logica NOT: Inverter

→ Inverter come mattone fondamentale

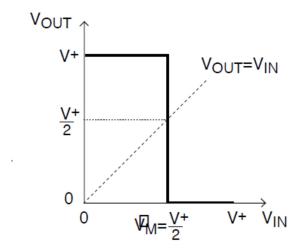

# Caratteristica di trasferimento: Inverter ideale

$V_{\scriptscriptstyle M}$ : tensione per cui  $V_{\scriptscriptstyle in} = V_{\scriptscriptstyle out}$

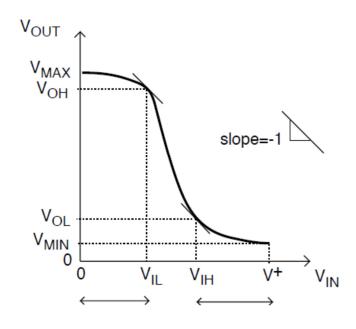

# Caratteristica di trasferimento: Inverter reale

Intervallo di V<sub>in</sub>

Intervallo di V<sub>in</sub>

che da' V<sub>out</sub> = 1

che da'  $V_{out} = 0$

$V_{IL}, V_{IH}$ : Livelli di ingresso min, max per i quali la pendenza della curva di trasferimento =-1  $V_{OL}, V_{OH}$ : Livelli di uscita min, max per i quali la pendenza della curva di trasferimento =-1

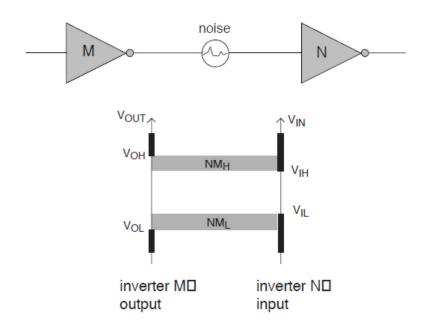

Condizioni in figura: M pilota correttamente N

## Margine di rumore:

$egin{array}{ll} V_{OH} - V_{IH} & {

m mdr} & {

m 'alto'} \\ V_{IL} - V_{OL} & {

m mdr} & {

m 'basso'} \end{array}$

→ Margine di rumore elevato = Garanzia di funzionamento corretto

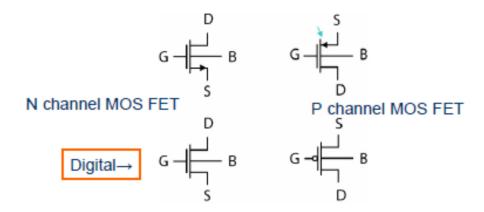

# MOS usati come interruttori:

NMOS ON per VG +va PMOS ON per VG -va

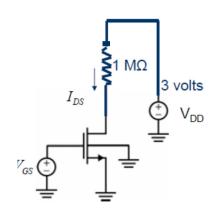

# Inverter NMOS:

# Problemi inverter NMOS/PMOS:

- $\rightarrow$  Per input *HIGH*, output ~1.2V

- → Stadio successivo pilotato da un *LOW* troppo alto

# Inoltre:

R grandi: difficili e non benvenute

$$I_{LOW} \sim 3\mu A \rightarrow P_{inv} \sim 10\mu W \rightarrow P_{tot} \sim 1~W/10^5 transistor$$

(1 CPU di oggi ~ 10kW!)

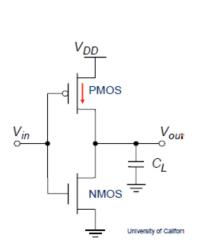

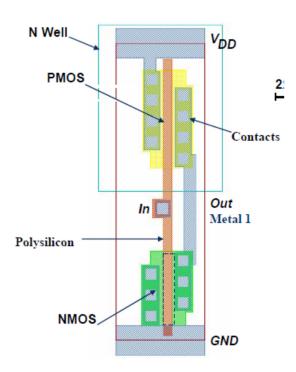

## **Inverter CMOS:**

## Caratteristica principale:

Staticamente, corrente nulla  $\rightarrow$  Consumo statico  $\sim 0$

Lunghezza del gate = Lunghezza del canale

Uguale per NMOS e PMOS

Larghezza del gate = Larghezza del canale

Diversa per NMOS e PMOS, per avere stessa corrente di drain in presenza di diverse mobilita' per elettroni e lacune

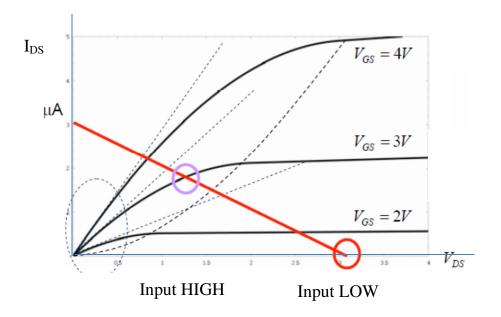

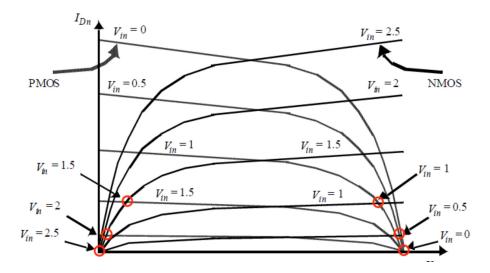

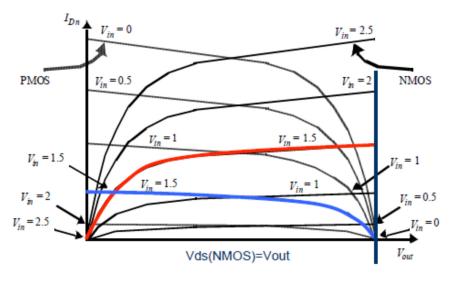

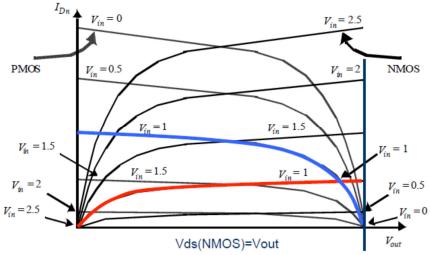

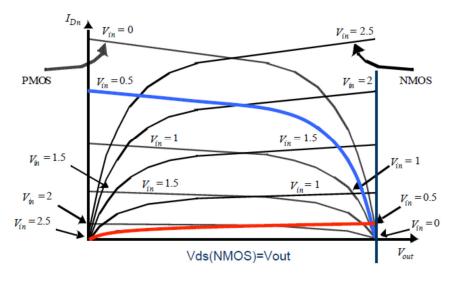

## Caratteristiche di uscita per NMOS e PMOS:

Corrente di drain (N) vs tensione fra drain e source

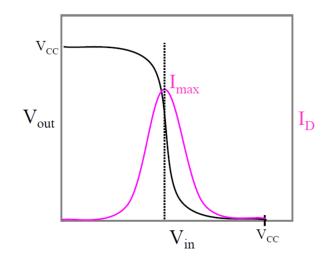

Valori di corrente vs tensione NMOS/PMOS per diversi  $V_{in}$  Circoletti rossi:  $V_{out}$  = Tensione comune di NMOS e PMOS  $\rightarrow$  Ricostruzione della relazione  $V_{out}$  vs.  $V_{in}$

$$V_{in} = \begin{cases} 0 \\ V_{DD} \end{cases} \rightarrow V_{out} = \begin{cases} V_{DD} \\ 0 \end{cases} \text{ OK}$$

$\text{Inoltre: } V_{\scriptscriptstyle in} \lesssim V_{\scriptscriptstyle DD} \to V_{\scriptscriptstyle out} \gtrsim 0, \ \ V_{\scriptscriptstyle in} \gtrsim 0 \to V_{\scriptscriptstyle out} \lesssim V_{\scriptscriptstyle DD}$

Ossia:  $V_{out} \sim \text{invariata per } V_{in} \neq \text{da valori nominali}$

$\rightarrow$  'Margine di rumore' elevato OK

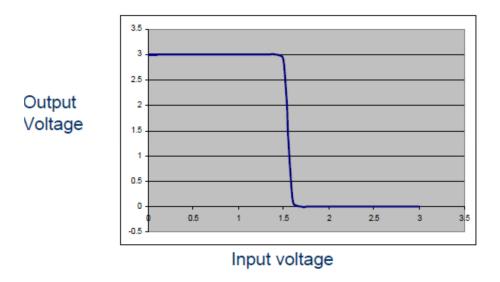

# Risposta in/out di un inverter 'ideale':

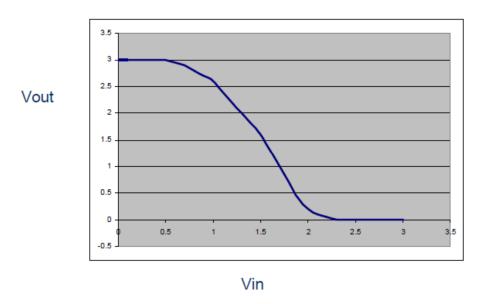

# Risposta in/out di un inverter CMOS:

# Infatti:

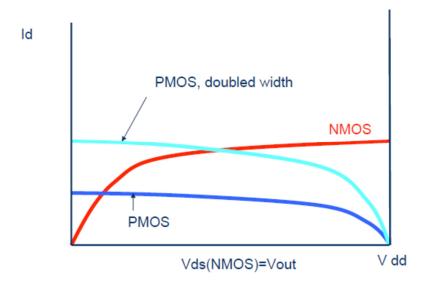

# Caratteristiche di uscita per NMOS e PMOS: fattore $\sim$ 2 in larghezza canale garantisce simmetria

$V_{\scriptscriptstyle M}$  tensione di drain (comune) t.c.  $V_{\scriptscriptstyle in}=V_{\scriptscriptstyle out}$

## Corrente per NMOS

$$I_{Dn} = v_{sat,n} W_n C_{0x} \left( V_M - V_{Tn} \right)^2 \left( 1 + \lambda_n V_M \right)$$

#### Corrente per PMOS

$$\begin{split} I_{Dp} &= -I_{Dn} = v_{sat,p} W_n C_{0x} \left( V_{DD} - V_M + V_{Tp} \right)^2 \left( 1 + \lambda_p \left( V_{DD} - V_M \right) \right) \\ g_n &= v_{sat,p} W_n C_{0x} \\ g_p &= v_{sat,p} W_p C_{0x} \end{split}$$

## Trascurando i $\lambda$ :

$$v_{sat,p}W_{p}C_{0x}\left(V_{DD}-V_{M}+V_{Tp}\right)^{2} \approx v_{sat,n}W_{n}C_{0x}\left(V_{M}-V_{Tn}\right)^{2}$$

$$\rightarrow g_{p}\left(V_{DD}-V_{M}+V_{Tp}\right)^{2} \approx g_{n}\left(V_{M}-V_{Tn}\right)^{2}$$

$$\rightarrow V_{DD}-V_{M}+V_{Tp} \approx \sqrt{\frac{g_{n}}{g_{p}}}\left(V_{M}-V_{Tn}\right)$$

$$\rightarrow V_{M}\left(1+\sqrt{\frac{g_{n}}{g_{p}}}\right) \approx \sqrt{\frac{g_{n}}{g_{p}}}V_{Tn}+V_{Tp}+V_{DD}$$

$$\rightarrow V_{M} \approx \frac{\sqrt{\frac{g_{p}}{g_{n}}}\left(V_{DD}+V_{Tp}\right)+V_{Tn}}{1+\sqrt{\frac{g_{p}}{g_{n}}}}$$

## Nessuna potenza dissipata staticamente

Ma: potenza dissipata dinamicamente

- → Durante le transizioni

- → Carica e scarica del carico capacitivo

$$\left(\leftarrow C_{out}\left(\text{stadio }n\right) + C_{in}\left(\text{stadio }n+1\right)\right)$$

$$\begin{split} i_L &= C_L \frac{dv_O}{dt} \quad \text{corrente nella capacita'} \\ P_P &= i_L V_{DS} = i_L \left( V_{DD} - V_O \right) \quad \text{Pot. istantanea dissipata dal PMOS} \\ E_P &= \int_0^\infty P_P \left( t \right) dt = \int_0^\infty C_L \left( V_{DD} - V_O \right) \frac{dv_O}{dt} dt \quad \text{Energia} \\ &\to E_P = \int_0^{V_{DD}} C_L \left( V_{DD} - V_O \right) dv_O = C_L V_{DD}^2 - \frac{1}{2} C_L V_{DD}^2 = \frac{1}{2} C_L V_{DD}^2 \\ &\to E_N = \frac{1}{2} C_L V_{DD}^2 \quad \text{En. dissipata nel NMOS} \end{split}$$

Pot. dissipata:

$$P = fE_T = fC_L V_{DD}^2$$

$\rightarrow E_T = C_L V_{DD}^2$  En. totale dissipata

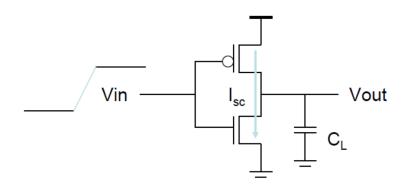

# Inoltre:

Passaggio di corrente nell'inverter durante le transizioni

Pot. dissipata

$$P_{SC} \simeq V_{DD} I_{\mathrm{max}} \frac{t_{sal} + t_{disc}}{2} f$$

## Inoltre:

Piccola potenza dissipata staticamente (correnti residue)

# Totale:

$$P_{tot} = fC_L V_{DD}^2 + V_{DD} I_{\text{max}} \frac{t_{sal} + t_{disc}}{2} f + P_{stat}$$

# Esempi di reti logiche CMOS: